[컴퓨터 구조] 레지스터와 마이크로 연산

레지스터에 저장된 데이터로 실행되는 동작을 마이크로 연산이라고 한다.

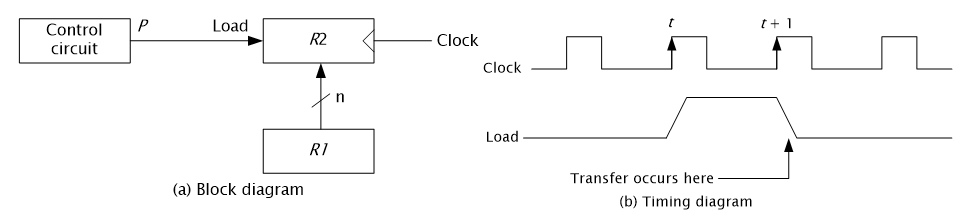

레지스터들의 종류를 간단하게 정리하자.

MAR : Memory Address Register

PC : Program Counter

IR : Instruction Register

R1 : Processor Register

DR : Data Register

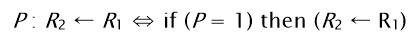

제어 명령은 위와 같은 형태로 주어진다.

P는 0또는 1을 가지는 변수로 P가 1일 때 레지스터 R1의 값을 레지스터 R2로 전달하라는 의미이다.

R2의 로드 입력은 제어 변수 P에 연결돼있고, 논리회로의 클럭과 동기되어 동작한다.

t+1 에서 P값이 로드되고 t+1 이후 다음 상승 모서리에서 실제 전송이 발생한다.

read와 write 모두 ← 연산으로 처리한다.(DR ← M[AR] / M[AR] ← R1 / M은 메모리 워드)

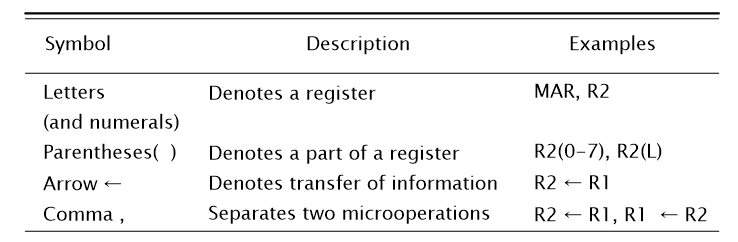

레지스터간의 정보 전송은 버스 시스템을 사용해서 처리한다.

버스는 데이터가 전송되는 통로 역할을 하고, 한 번에 하나의 전송만 이루어지도록 설계됐다. (두 개 이상이 전송되면 회로가 타버린다)

버스는 MUX와 Three-State-Buffer로 구현될 수 있다.

1. Multiplexer

버스는 네 개의 데이터 입력과 두 개의 선택 입력을 가지는 멀티플렉서들로 구성돼있다.

선택 입력 S0과 S1의 값에 따라 선택되는 레지스터가 달라진다. (S0과 S1이 제어 변수 역할을 한다)

n비트를 가지는 k개의 레지스터를 MUX해서 버스 시스템을 만드려면 n개의 k * 1 MUX가 필요하다.

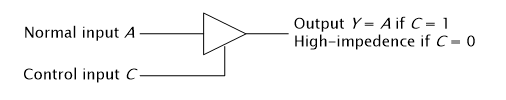

2. Three-State-Buffer

제어 입력이 1이면 보통 버퍼와 같이 입력과 출력이 같다.

제어 입력이 0이면 출력이 끊어지고 high-impedance state가 된다. (출력이 끊어져 로딩되지 않는다)

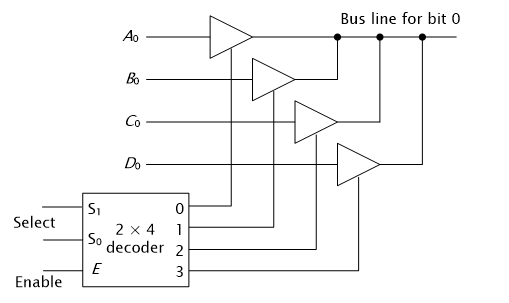

디코더를 사용한다.

Enable 값이 1일 때 선택 입력 S1, S0에 따라 한 순간에 하나의 Three-State-Buffer만 활성화되도록 한다.

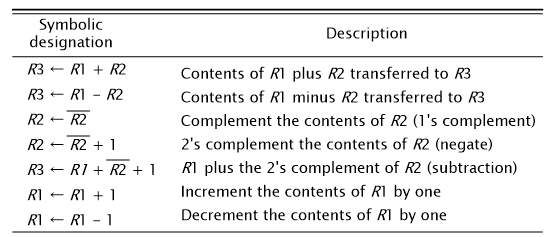

산술 연산을 구현하려면 몇 가지 하드웨어가 필요하다.

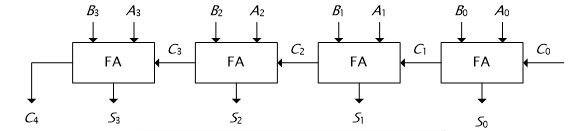

논리회로에서 많이 접했던 이진 가산기이다.

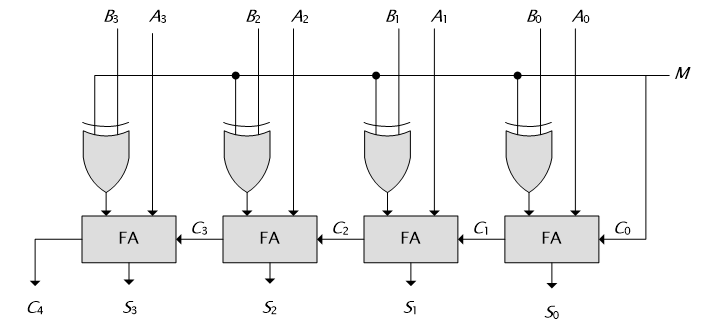

역시 논리회로에서 많이 접했던 이진 감가산기이다.

M이 0이면 가산기로, M이 1이면 감산기로 작동한다.

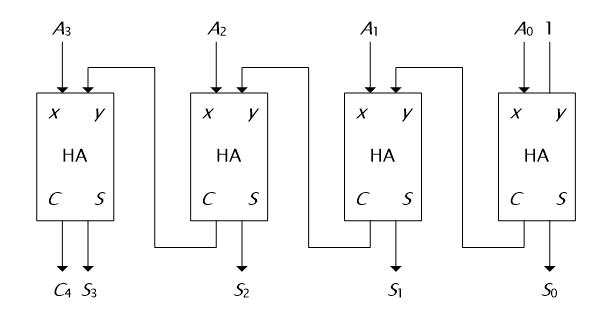

이진 인크리멘터 (Binary Incrementer) 이다.

Half Adder를 사용하고, 레지스터의 값에 1을 더할 때 사용된다.

논리 연산은 마이크로 연산에서 사용되는 경우와 제어함수에서 사용되는 경우가 서로 다르다.

마이크로 연산에서는 비트 단위로 연산을 수행하고, 대부분의 컴퓨터에서는 AND / XOR / OR / 보수 정도만 사용한다.

시프트 연산은 (https://13months.tistory.com/487) 를 참고하자.

산술 시프트에서 부호 비트인 MSB는 시프트되지 않는다.

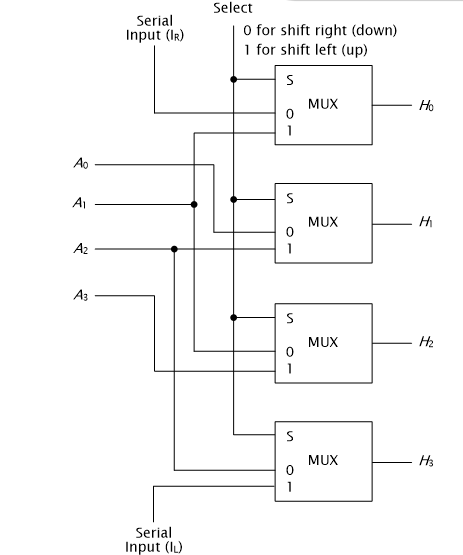

클럭 펄스에 상관없이 조합 회로만으로 시프트 연산을 구현하는 편이 합리적이다.

선택 입력 S가 0이면 오른쪽으로, 1이면 왼쪽으로 시프트한다.

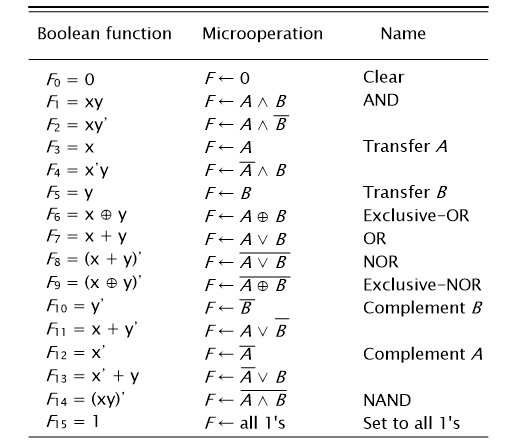

컴퓨터에서는 공용 연산 장치인 산술 논리 장치 (ALU) 를 사용해 연산을 한 군데에서 처리한다.

ALU는 조합 회로로 설계되어있어 데이터 전송이 하나의 클럭 펄스에 수행된다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [컴퓨터 구조] 기본 컴퓨터 프로그래밍 (0) | 2022.10.09 |

|---|---|

| [컴퓨터 구조] 기본 컴퓨터의 구조와 설계 (2) | 2022.10.04 |

| [컴퓨터 구조] 데이터의 표현 (0) | 2022.10.02 |

댓글

이 글 공유하기

다른 글

-

[컴퓨터 구조] 기본 컴퓨터 프로그래밍

[컴퓨터 구조] 기본 컴퓨터 프로그래밍

2022.10.09 -

[컴퓨터 구조] 기본 컴퓨터의 구조와 설계

[컴퓨터 구조] 기본 컴퓨터의 구조와 설계

2022.10.04 -

[컴퓨터 구조] 데이터의 표현

[컴퓨터 구조] 데이터의 표현

2022.10.02